16.构建晶体管之间连接电路

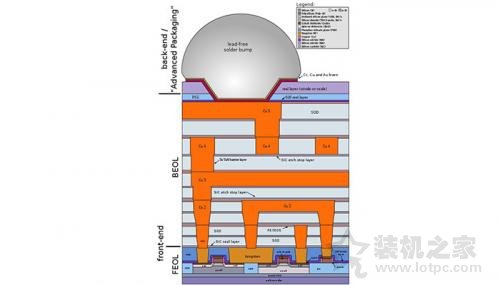

经过漫长的工艺,数以十亿计的晶体管已经制作完成。剩下的就是如何将这些晶体管连接起来的问题了。同样是先形成一层铜层,然后光刻掩模、蚀刻开孔等精细操作,再沉积下一层铜层。。。。。。这样的工序反复进行多次,这要视乎芯片的晶体管规模、复制程度而定。最终形成极其复杂的多层连接电路网络。

由于现在IC包含各种精细化的元件以及庞大的互联电路,结构非常复杂,实际电路层数已经高达30层,表面各种凹凸不平越来越多,高低差异很大,因此开发出CMP化学机械抛光技术。每完成一层电路就进行CMP磨平。

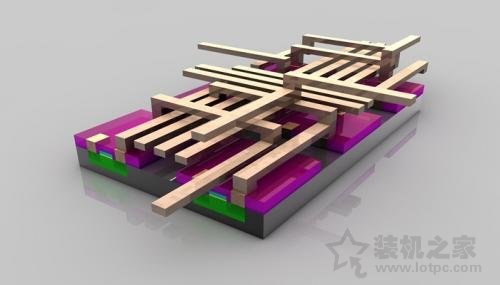

另外为了顺利完成多层Cu立体化布线,开发出大马士革法新的布线方式,镀上阻挡金属层后,整体溅镀Cu膜,再利用CMP将布线之外的Cu和阻挡金属层去除干净,形成所需布线。

大马士革法多层布线

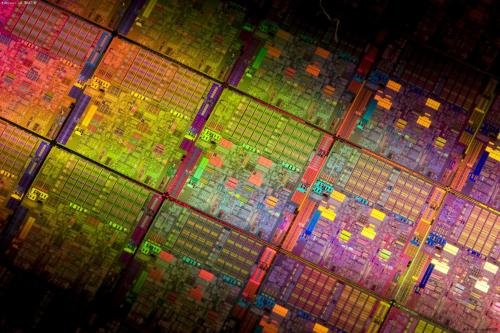

芯片电路到此已经基本完成,其中经历几百道不同工艺加工,而且全部都是基于精细化操作,任何一个地方出错都会导致整片晶圆报废,在100多平方毫米的晶圆上制造出数十亿个晶体管,是人类有文明以来的所有智慧的结晶。

后工程——从划片到成品销售

17. 晶圆级测试

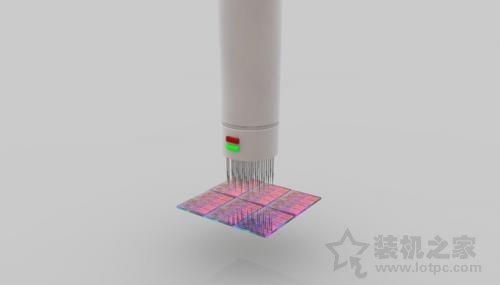

前工程与后工程之间,夹着一个Good-Chip/Wafer检测工程,简称G/W检测。目的在于检测每一块晶圆上制造的一个个芯片是否合格。通常会使用探针与IC的电极焊盘接触进行检测,传输预先编订的输入信号,检测IC输出端的信号是否正常,以此确认芯片是否合格。

由于目前IC制造广泛采用冗余度设计,即便是“不合格”芯片,也可以采用冗余单元置换成合格品,只需要使用激光切断预先设计好的熔断器即可。当然,芯片有着无法挽回的严重问题,将会被标记上丢弃标签。

18.晶圆切片、外观检查

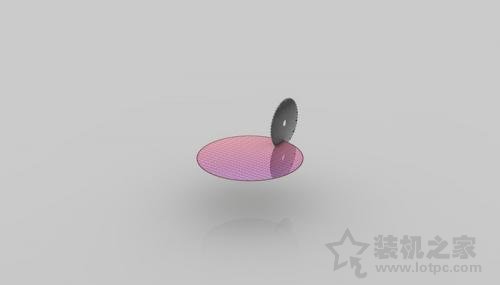

IC内核在晶圆上制作完成并通过检测后,就进入了划片阶段。划片使用的划刀是粘附有金刚石颗粒的极薄的圆片刀,其厚度仅为人类头发的1/3。将晶圆上的每一个IC芯片切划下来,形成一个内核Die。

裂片完成后还会对芯片进行外观检查,一旦有破损和伤痕就会抛弃,前期G/W检查时发现的瑕疵品也将一并去除。

未裂片的一个个CPU内核

19.装片

芯片进行检测完成后只能算是一个半成品,因为不能被消费者直接使用。还需要经过装片作业,将内核装配固定到基片电路上。装片作业全程由于计算机控制的自动固晶机进行精细化操作。